### 中国科学院大学网络空间安全学院专业必修课

2022-2023学年秋季学期

第三部分 CMOS门电路

授课团队:宋威

助 教: 马浩

#### CMOS门电路

现在的超大规模逻辑电路 (VLSI: Very Large Scale Integration) 基本都是由CMOS门电路构成的(数字部分)。

在这门课中,我们只介绍CMOS门电路,有关TTL门电路或者BiMOS门电路,请参阅教材第三章的对应部分。有关使用CMOS/TTL电路构造模拟电路,请参考模拟电路的相关教材。

**CMOS:** Complementary metal-oxide-semiconductor

互补MOS工艺,或者互补金属氧化物半导体工艺。

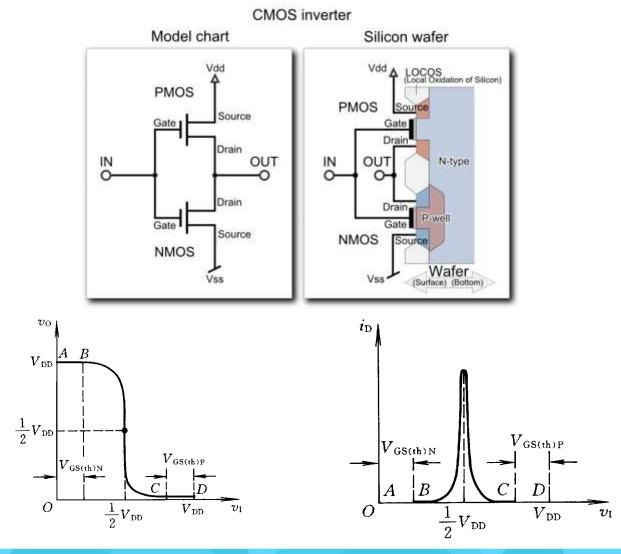

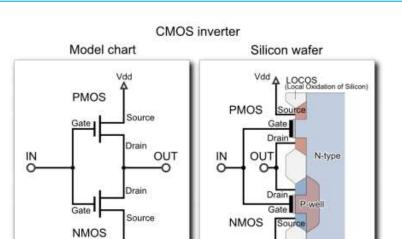

#### ○CMOS反门就是用CMOS工艺构造的反门

## CMOS反门

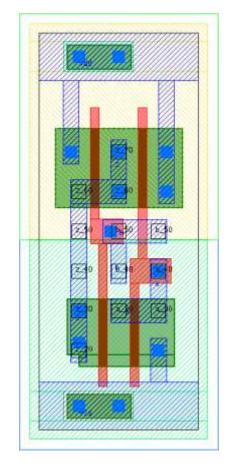

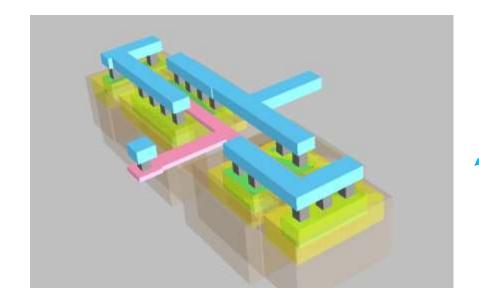

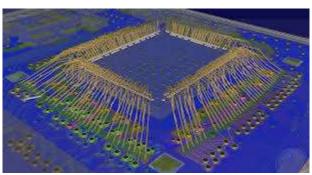

版图

Wafer (Surface) (Bottom)

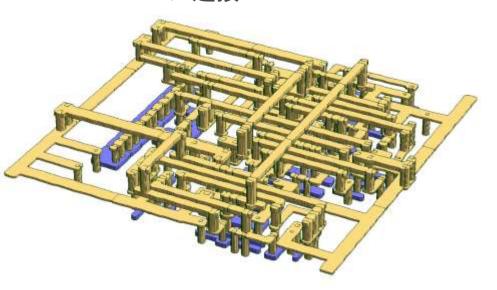

3D效果

反门

三输入与非门

寄存器

- 高度一样,一边VDD一边GND。

- 根据复杂度的区别,宽度不一样。

- VDD一边都是PMOS晶体管, GND一边都是NMOS晶体管

- 晶体管之间用poly或者第一层金属层(M1)连接

- 第一层金属宽度一样,可以拐弯(越来越难)

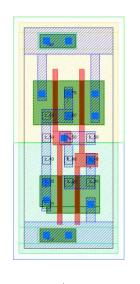

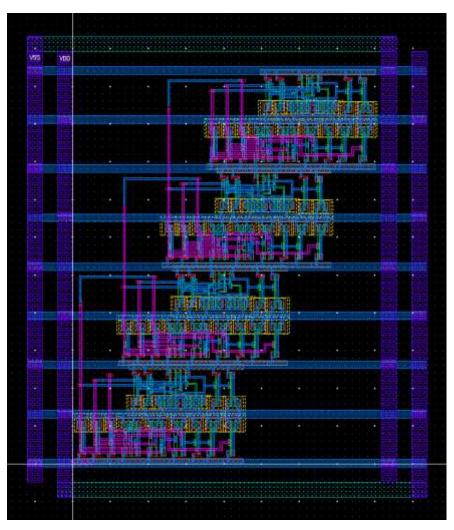

## CMOS门电路

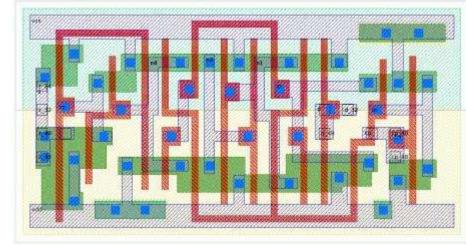

- 利用多个CMOS门搭建更复杂的CMOS 电路。

- CMOS门被放置在一排一排平行的row 中,相邻的row共享VDD或GND。

- 相邻row的CMOS门方向相反。

- CMOS门之间通过多层金属导线连接

- 底层的金属导线较细,用于信号连接。

- 不同层的金属导线方向正交。

- 不同层之间用via连接。

- 顶层的导线较粗,用于电源( VDD/GND)连接。

Booth 乘法器

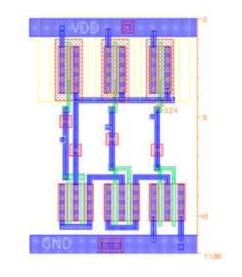

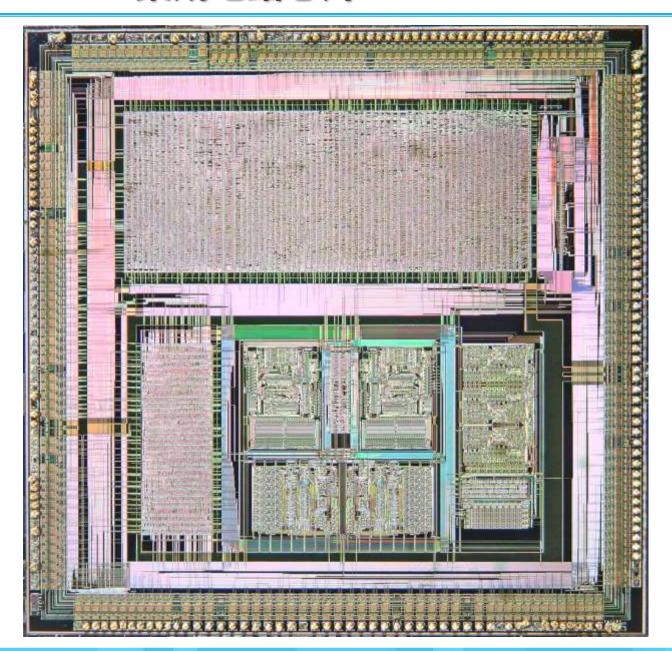

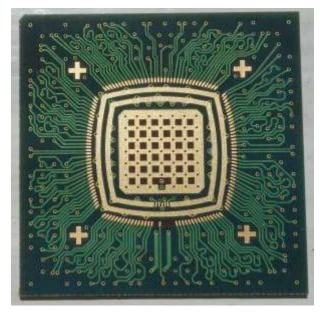

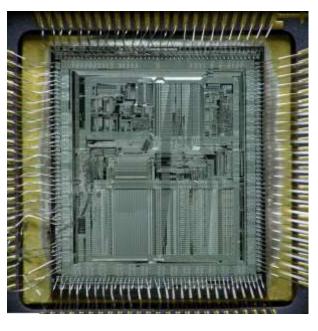

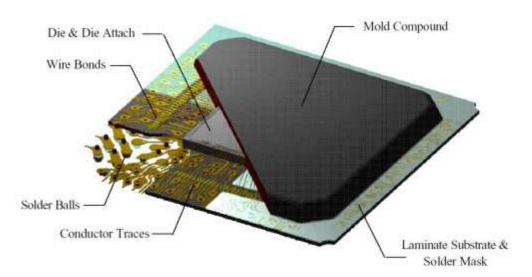

## CMOS集成电路芯片

- die

- 放置IP, 布局布线

- IO pad

- Power ring/rail

- routing

## CMOS集成电路芯片

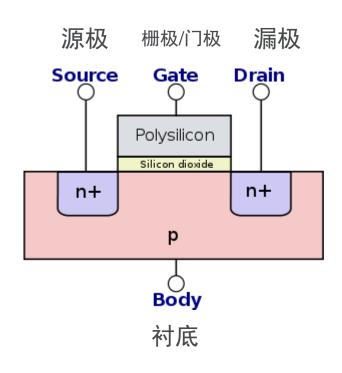

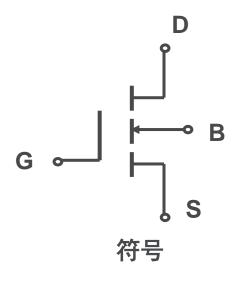

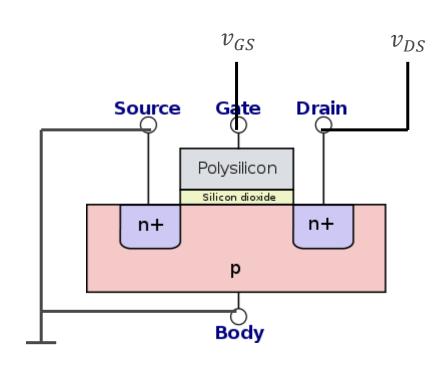

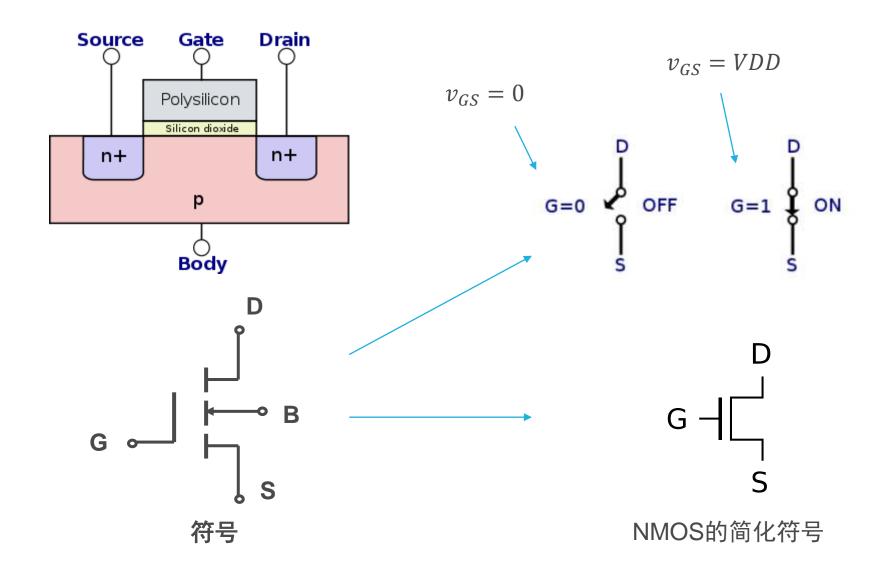

## MOS晶体管—NMOS

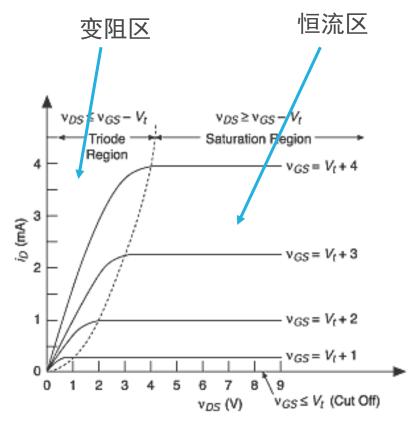

### NMOS基本特性

在数字电路中,NMOS管工作在变阻区和截止区。状态稳定时, $v_{GS}$ 要么接近于0,要么大于阈值电压 $v_t$ ,电流 $i_{DS}$ 总是接近于0。

当 $v_{GS} > 0$ 时,衬底中的电子被G吸引,形成N型沟道。联通S和D。

### NMOS开关电路

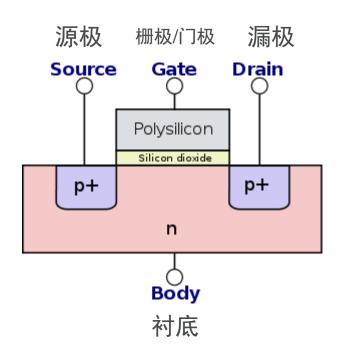

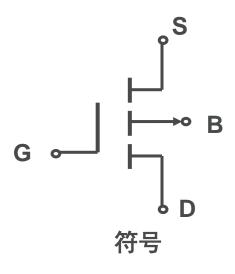

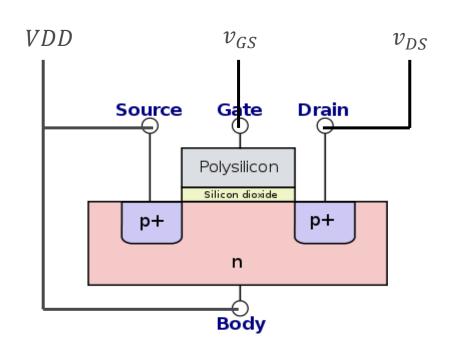

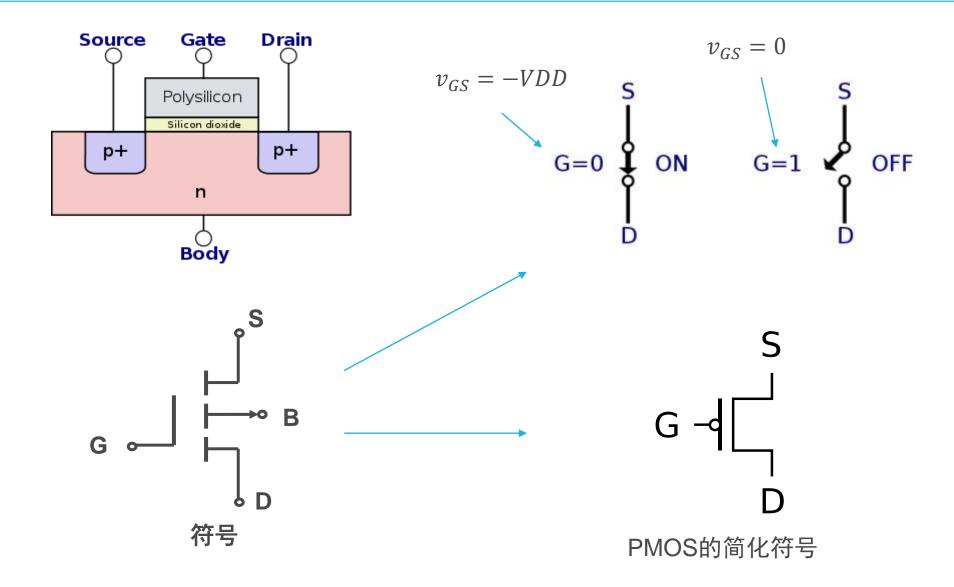

## MOS晶体管—PMOS

### PMOS基本特性

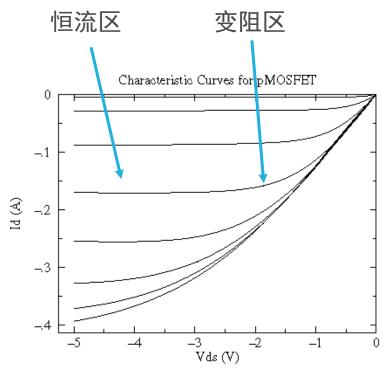

在数字电路中,PMOS管工作在变阻区和截止区。状态稳定时, $v_{GS}$ 要么接近于0,要么小于阈值电压  $-v_t$ ,电流 $i_{DS}$ 总是接近于0。

当 $v_{GS} < 0$ 时,衬底中的空穴被G吸引,形成P型沟道。连通S和D。

这里的描述和教材上的略有区别,注意这里连的是VDD,书上用的GND。

### PMOS开关电路

### MOS管总结

- **ONMOS**

- $\bigcirc$ 当 $v_{GS} > 0$ 时D和S导通。

- ○相当于一个门级在高电压(1状态)时闭合的开关电路。

- **OPMOS**

- $\bigcirc$ 当 $v_{GS} < 0$ 时D和S导通。

- ○相当于一个在低电压(0状态)时闭合的开关电路。

- ○在数字电路中,MOS管工作在截止区和可变电阻区

- ○非闭即开

- ○不讨论电压电流模型

- ○不讨论可变电阻区/恒流区的物理特性

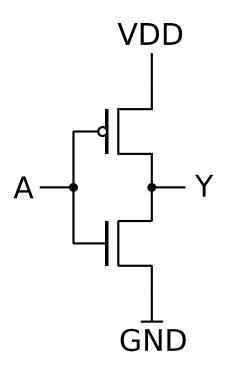

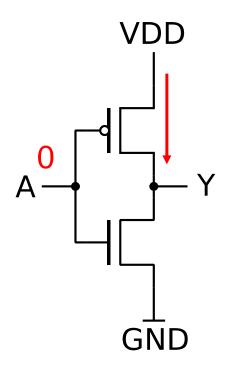

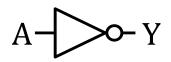

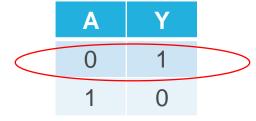

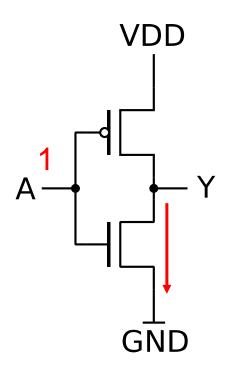

## CMOS反门

| Α | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

## CMOS反门—0

## CMOS反门—1

| Α | Y |  |

|---|---|--|

| 0 | 1 |  |

| 1 | 0 |  |

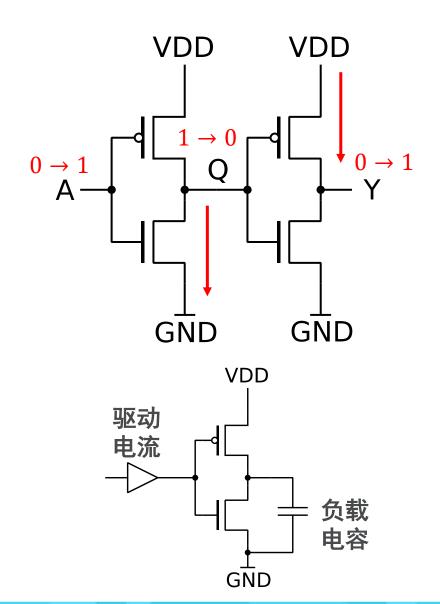

## CMOS反门—电压电流特性

#### CMOS反门总结

- ○互补型结构

- ○所有的CMOS门电路都是互补型结构

- ○VDD接PMOS, GND接NMOS

- ○工作在截止区和可变电阻区

- ○状态稳定(输入输出无变化)时电流极小

- ○状态改变时产生从VDD到GND的瞬时大电流

- ○驱动和负载模型

- ○驱动主要讨论电流供给能力,即给电容充电的强度

- ○负载主要是各门电路的门级到源极的等效电容

- ○驱动和负载决定了门的反应时间 (transition time)

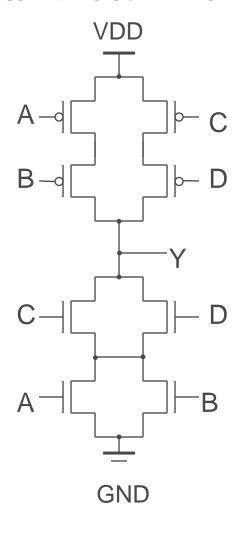

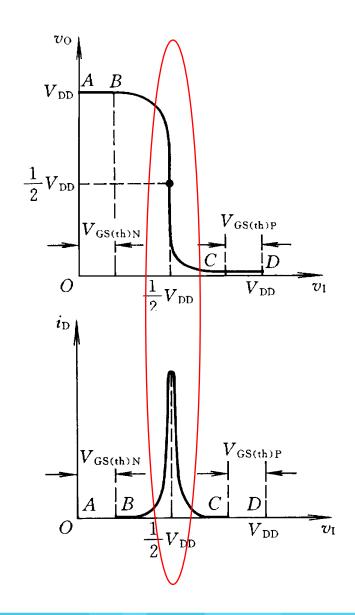

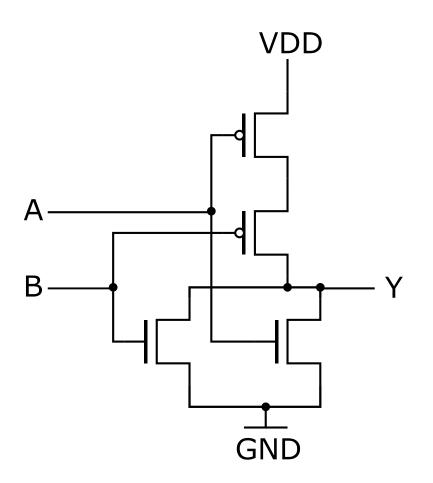

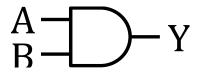

# CMOS与非门

| Α | В | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

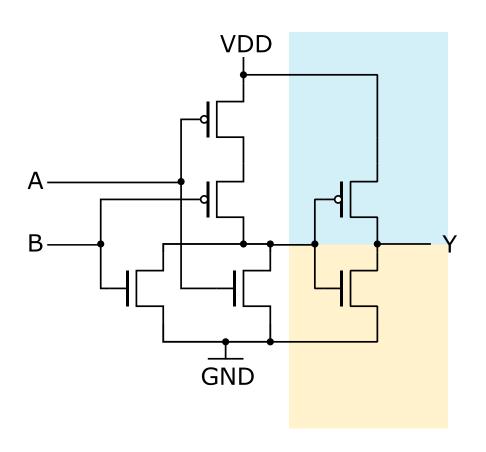

## CMOS或非门

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

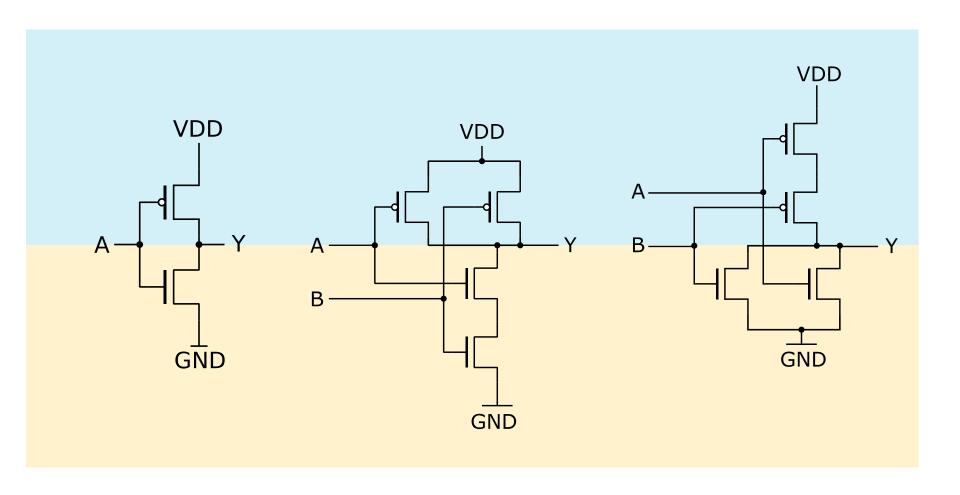

## CMOS反门、与非门、或非门

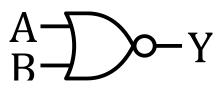

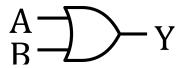

## CMOS与门

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

# CMOS或门

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

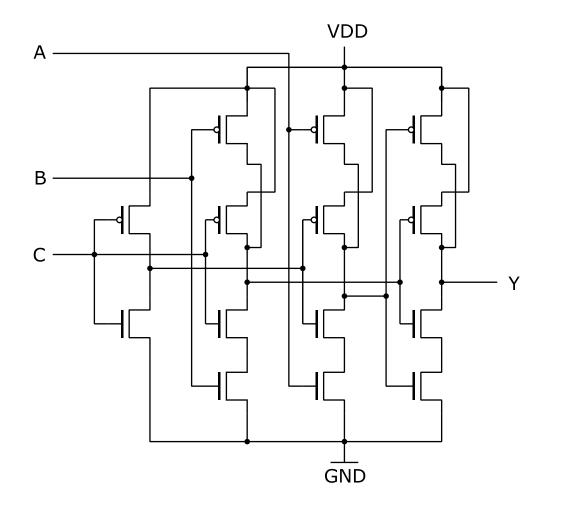

## CMOS门电路识别—真值表

| Α | В | С | Υ |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

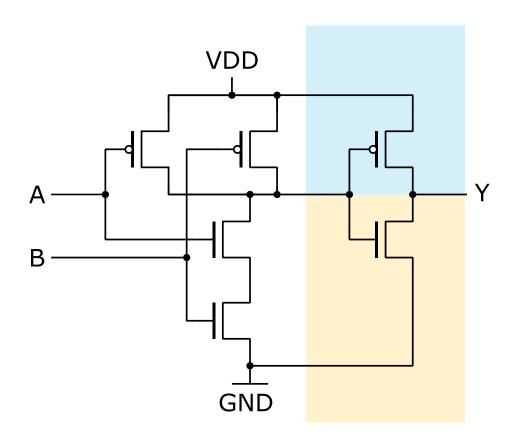

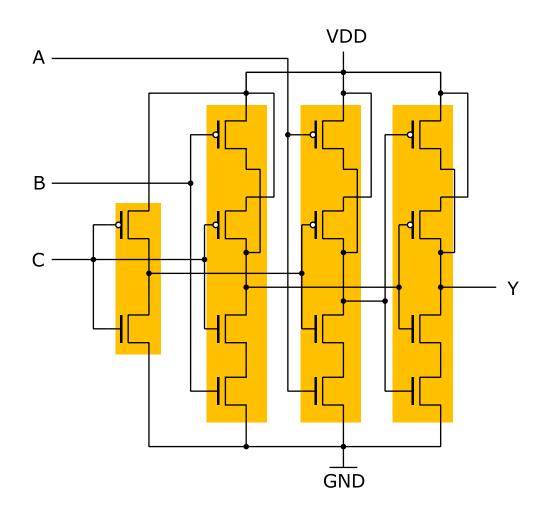

## CMOS门电路识别—门识别

### CMOS门电路总结

- ○互补型结构

- ○所有的CMOS门电路都是互补型结构

- ○VDD接PMOS, GND接NMOS

- ○MOS管的总数量一定是偶数

- ○PMOS和NMOS的结构一定是对应存在的

- ○判别一个较复杂门电路的功能

- ○利用真值表

- ○利用简单门的判别

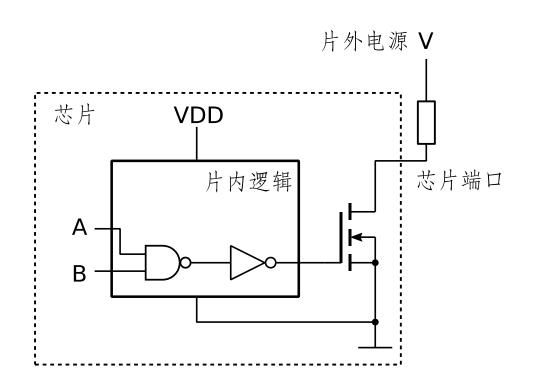

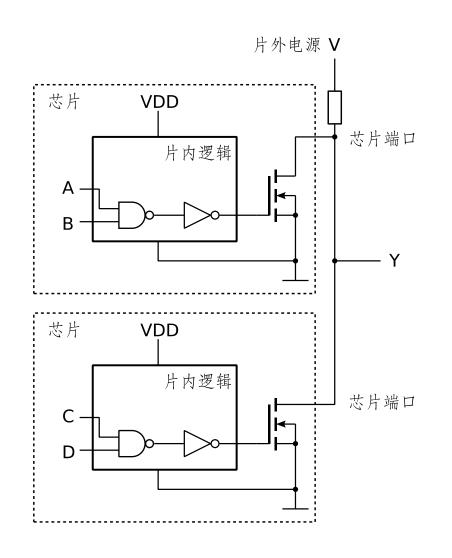

## 其他电路:漏极开路输出门 (OD门)

| Α | В | Y |

|---|---|---|

| 0 | 0 | V |

| 0 | 1 | V |

| 1 | 0 | V |

| 1 | 1 | 0 |

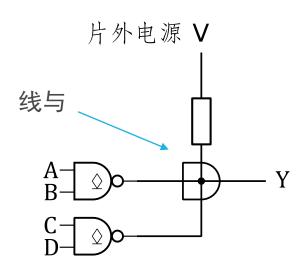

## 漏极开路输出门 (OD门) — 使用

- ○漏极开路

- ○实现片外的电压转换

- ○实现片外片与逻辑

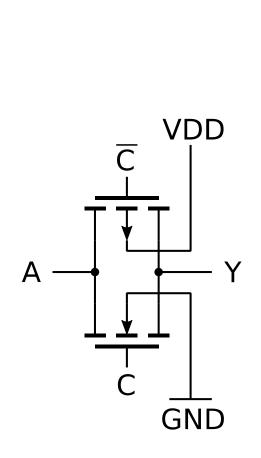

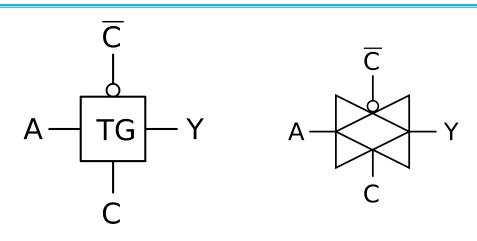

### 其他电路: CMOS传输门

| Α | С | Y |

|---|---|---|

| 0 | 1 | 0 |

| 1 | 1 | 1 |

| 0 | 0 | Z |

| 1 | 0 | Z |

- 片内可以使用,必须成对出现

- 有时候可以用于简化电路

- Y和A之间会产生一个压降,相当于电阻(电阻型负载)

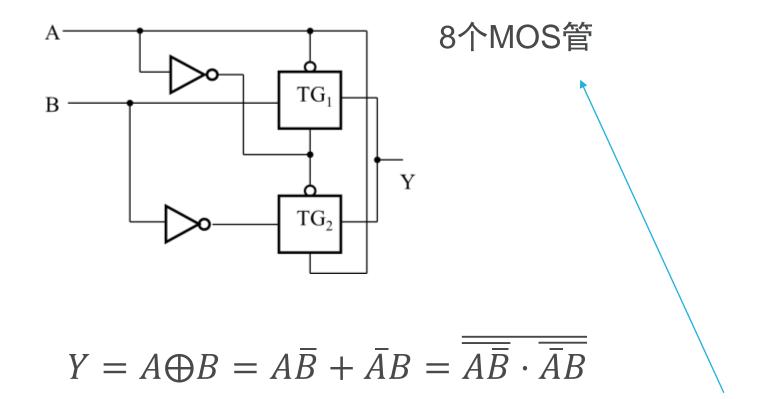

### CMOS传输门— 简化异或门

2个反门, 3个二输入与非门,  $2 \times 2 + 3 \times 4 = 16$ 个MOS管。

宋威

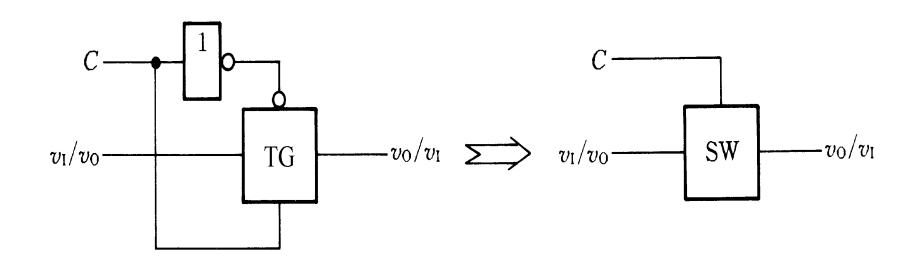

## CMOS传输门— 开关电路

闭合时双向导通

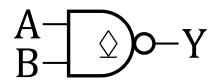

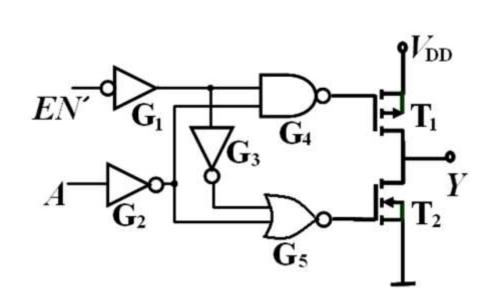

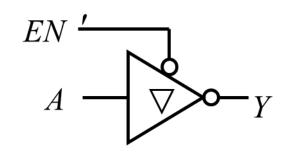

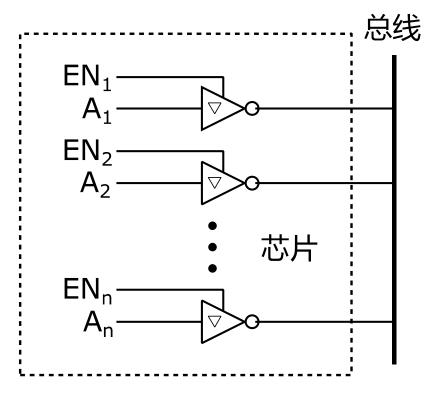

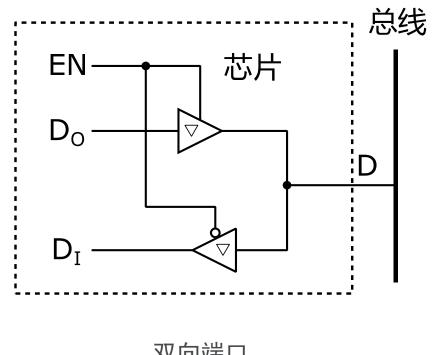

### 其他电路: CMOS三态输出

#### 逻辑符号

| Α | EN | Y |

|---|----|---|

| 0 | 0  | 1 |

| 1 | 0  | 0 |

| 0 | 1  | Z |

| 1 | 1  | Z |

- 一般只能在芯片的I/O端口上使用。

- 当不导通时,输出高阻。

### CMOS三态输出-

片外总线

双向端口

### 总结:考试范围

- ○集成电路芯片 (非考试范围)

- ○理解集成电路芯片的大概内部结构

- **○MOS晶体管**

- ○NMOS和PMOS的构造、基本电流电压特性

- ○CMOS门电路

- ○反相器的内部构造、基本电流电压特性

- ○基本门电路的内部构造

- ○从CMOS结构识别电路功能

- ○其他的门电路

- ○漏极开路(OD)电路

- ○传输门

- ○三态门

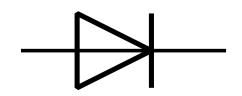

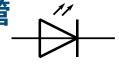

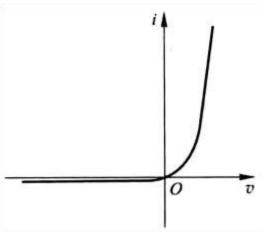

## 二极管

#### ○半导体二极管 (diode)

- ○单向导通

- ○关闭时电流极小

- ○开启时正向有一定压降和电阻效应

- ○一般不可忽略

- ○可用做开关电路和保护电路

- ○发光二极管

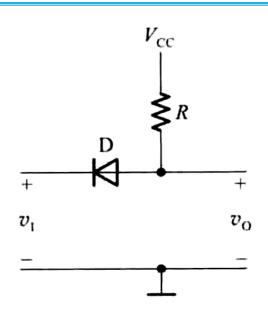

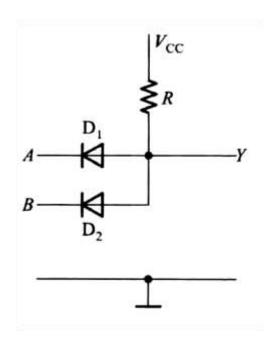

# 二极管构成的电路

#### ○二极管与门

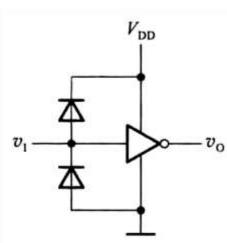

#### ○保护电路

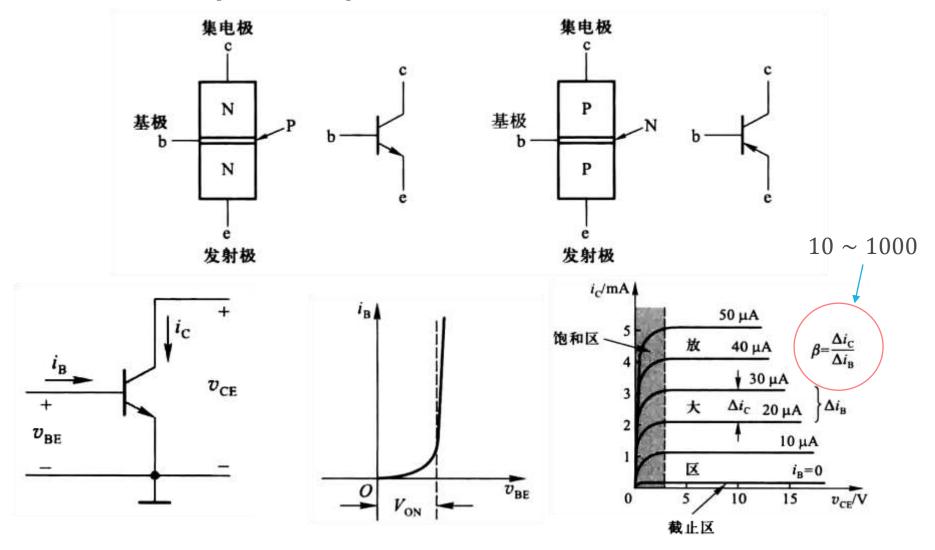

#### ○三极管 (transistor)

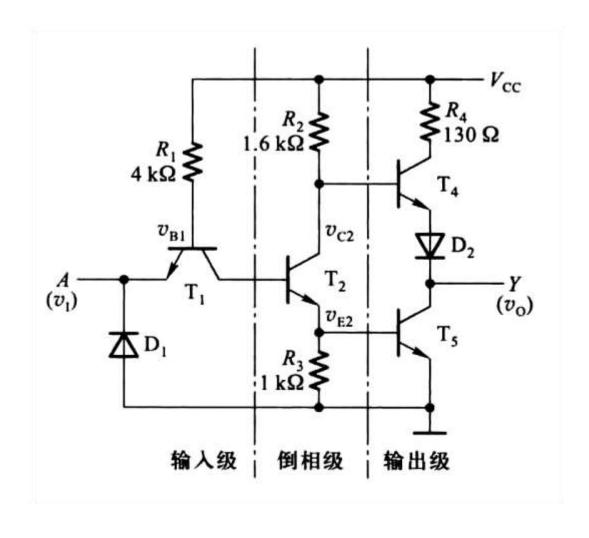

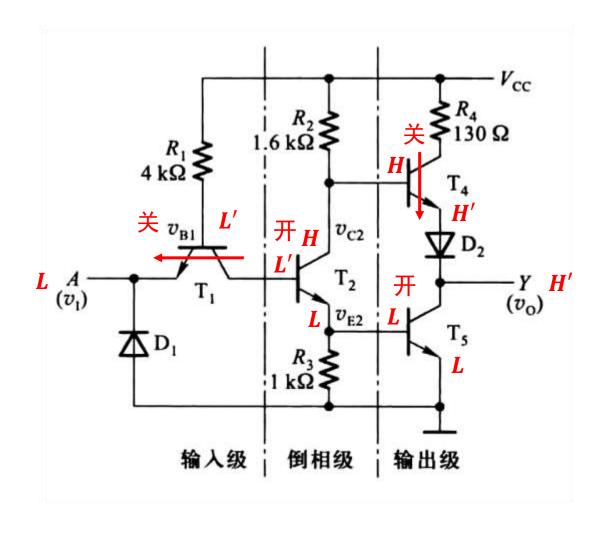

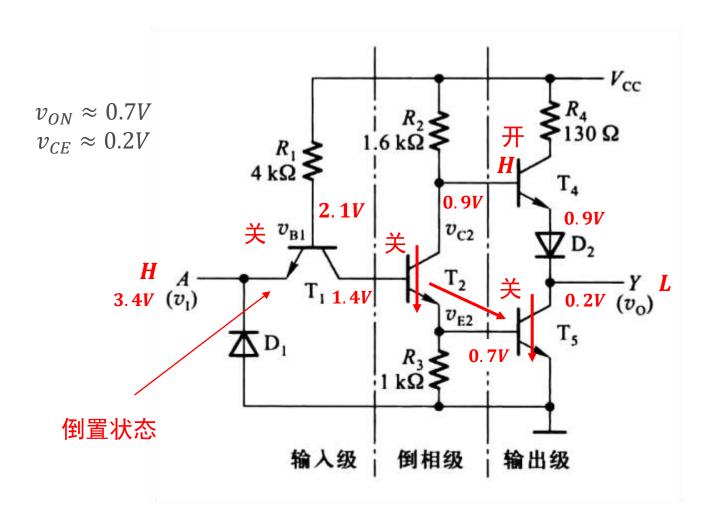

# 三极管组成的TTL电路

#### ○TTL (transistor-transistor-logic) 反相器

## 三极管组成的TTL电路

#### ○TTL (transistor-transistor-logic) 反相器

## 三极管组成的TTL电路

#### ○TTL (transistor-transistor-logic) 反相器

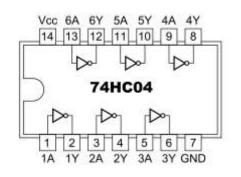

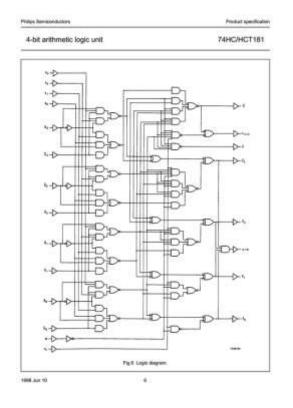

# CMOS集成电路模块系列

# CMOS集成电路模块系列

## CMOS集成电路模块系列

|        | VDD (V)  | I <sub>out</sub> (mA) | I <sub>in</sub> (μΑ) | $t_{pd}$ (ns) | <i>C<sub>in</sub></i> (pF) | <i>C<sub>pd</sub></i> (pF) |

|--------|----------|-----------------------|----------------------|---------------|----------------------------|----------------------------|

| 74HC   | 2~6      | -4~4                  | -1~1                 | 9             | 10                         | 20                         |

| 74HCT  | 4.5~5.5  | -4~4                  | -1~1                 | 14            | 10                         | 20                         |

| 74AHC  | 2~5.5    | -8~8                  | -1~1                 | 5.3           | 10                         | 12                         |

| 74AHCT | 4.5~5.5  | -8~8                  | -1~1                 | 5.5           | 10                         | 14                         |

| 74LVC  | 1.65~3.6 | -24~24                | -5~5                 | 3.8           | 5                          | 8                          |

| 74ALVC | 1.65~3.6 | -24~24                | -5~5                 | 2             | 3.5                        | 23                         |

- HC: high-performance CMOS 高性能 CMOS

- T: TTL compatible 和TTL电压兼容

- A: advanced 改进版

- LVC: low-voltage CMOS 低电压CMOS

## TTL集成电路模块系列

|       | I <sub>out</sub> (mA) | I <sub>in</sub> (mA) | $t_{pd}$ (ns) | P (mW) |

|-------|-----------------------|----------------------|---------------|--------|

| 74    | -0.4~16               | 0.04 ~ -1.0          | 9             | 10     |

| 74S   | -1.0~20               | 0.05 ~ -2.0          | 3             | 19     |

| 74LS  | -0.4~8                | 0.02 ~ -0.4          | 9.5           | 2      |

| 74AS  | -2.0~8                | 0.02 ~ -0.5          | 1.7           | 8      |

| 74ALS | -0.4~8                | 0.02 ~ -0.2          | 4             | 1.2    |

| 74F   | -1.0~20               | 0.02 ~ -1.6          | 3             | 4      |

• S: Schottky 肖特基

• L: Low-power 低功耗

• A: Advanced 改进版

• F: Fast 高速

# 任何问题?

第三章习题:

7, 8.

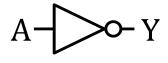

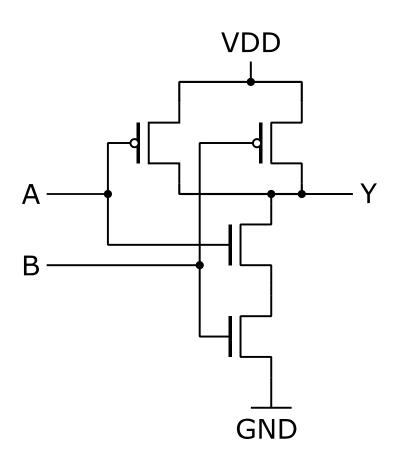

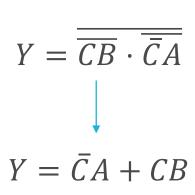

#### ○描述下面CMOS电路的逻辑表达式